收藏,持续更新!CMOS工艺流程详解说 |

您所在的位置:网站首页 › deep n well作用 › 收藏,持续更新!CMOS工艺流程详解说 |

收藏,持续更新!CMOS工艺流程详解说

|

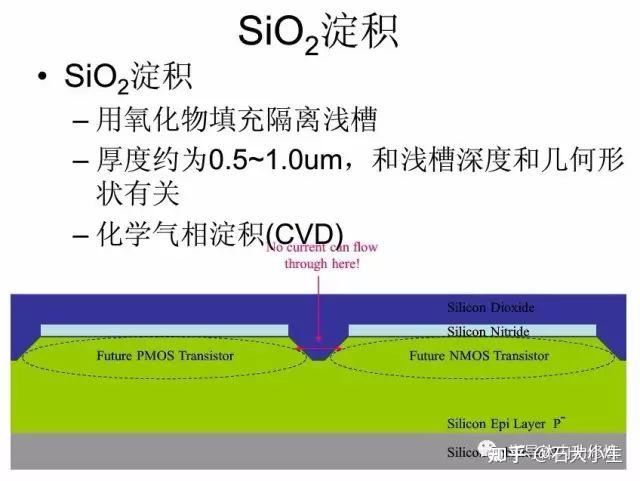

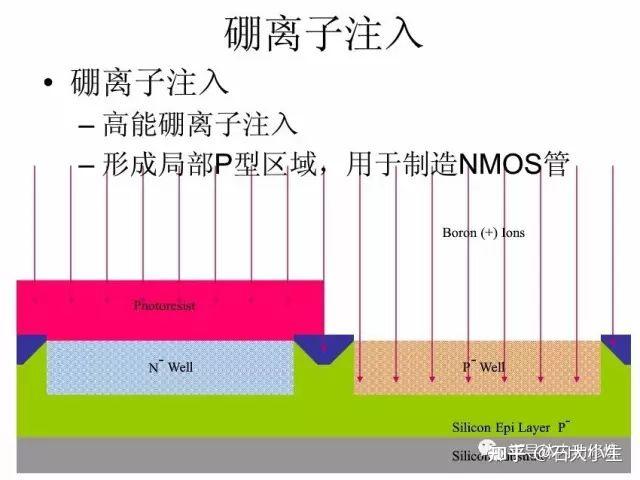

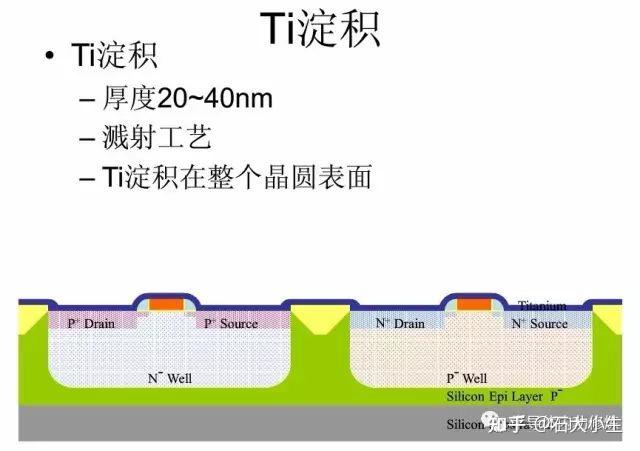

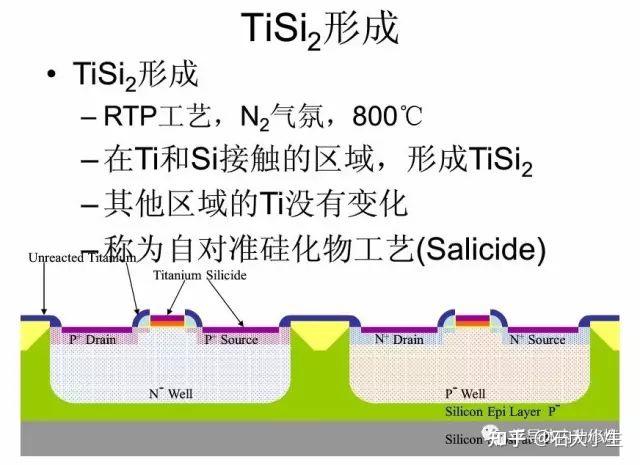

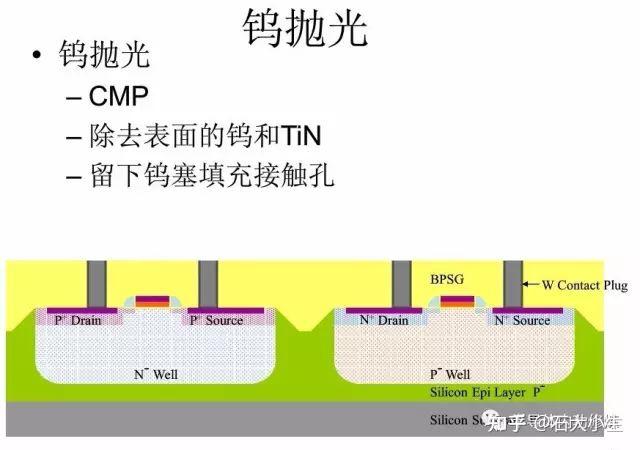

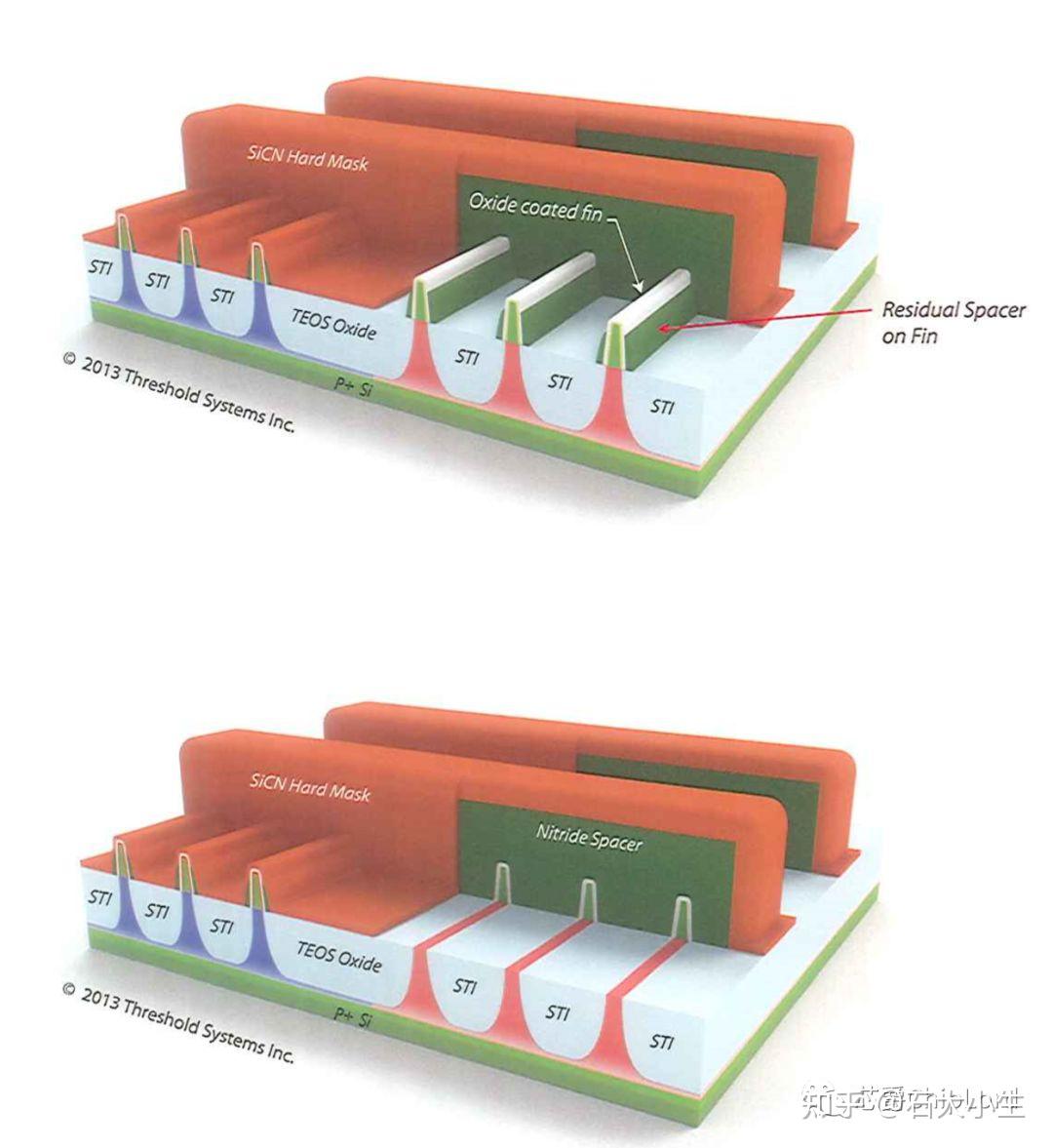

CMOS工艺流程介绍(最常规的一种,大家参考下,下次再发一种),欢迎关注 @石大小生 常规CMOS 1.衬底选择:选择合适的衬底,或者外延片,本流程是带外延的衬底;  2. 开始:Pad oxide氧化,如果直接淀积氮化硅,氮化硅对衬底应力过大,容易出问题;  接着就淀积氮化硅。  3. A-A层的光刻:STI(浅层隔离)  (1)A-A隔离区刻蚀:先将hard mask氮化硅和oxide一起刻掉;  (2)STI槽刻蚀:Si3N4的刻蚀菜单刻蚀硅速率过快,不好控制,需要分开刻蚀;  (3)刻蚀完成后去胶,为了节省空间,后面的层次去胶将会用一句话带过;  (4)STI用氧化硅填充:这里没有讲,其实刻蚀STI会对衬底造成损伤,一般要先长一层薄氧化层,然后再腐蚀掉的,这样可以消除表现损伤; STI填充:HDP高密度等离子淀积STI槽,用其他机器填充会提前将STI槽封死,里面会出现空洞,HDP机台是一遍淀积,一遍刻蚀,可以防止提前封口;  (5)简单的做法是直接CMP将二氧化硅磨平,但一般该步骤直接CMP会造成STI表面下陷,STI槽不满的情况,一般还会再加一层,将STI区域保护起来,将中间区域刻蚀掉,然后再CMP,这里简化处理。  (6)热磷酸腐蚀掉氮化硅,这个不叫常规;   4. Nwell光刻、注入:光刻前都有一层pad oxide,这里也没有画。  Nwell注入:一般要注一个阱,一个防传统注入,一个VT调节注入,三次注入分别对应深,中,浅,注入玩去胶,准备做Pwell注入;  5. Pwell光刻、注入:方式与Nwell类似,注入改为B注入,然后去胶,去胶后要将Nwell和Pwell一起推进,使两者有一定的结深和浓度梯度;     6. Gate栅的形成:腐蚀掉表现氧化层,再长一层牺牲氧化层,然后再腐蚀掉牺牲氧化层;   (1)栅氧化层生长:非常薄,质量非常关键,要控制好厚度,电荷,可动离子等;  (2)POLY淀积:淀积 Insu-Poly,或者后面掺杂后再光刻  (3)POLY光刻、刻蚀:光刻Gate,并刻蚀POLY,然后去胶;    (4)POLY氧化:作为SI3N4 spacer刻蚀的停止层;  7. NLDD/PLDD的形成: (1)NLDD光刻,注入,去胶;   (2)PLDD光刻,注入,去胶;   (3)Si3N4 spacer的刻蚀:氮化硅淀积及刻蚀   8. NSD/PSD形成: (1)NMOS的源漏注入:Si3N4 spacer挡住的区域NSD注入注不进去,因此NSD区域要离开gate一小段距离;   (2)PMOS源漏注入:做完PSD,一起做一次RTP来退回,激活离子。    到此,器件工艺完成了,平面图如下:  9. Salicide:Ti与硅形成低阻层Salicide;    只有与硅接触的T与硅反应了,其它区域Ti未反应可以腐蚀掉。  10.ILD淀积及contac形成: (1)BPSG淀积及CMP抛光。   (2)contact孔光刻即刻蚀:   W-plug:W塞淀积及CMP。     11. Metal-1淀积及光刻,刻蚀:     12. IMD淀积, CMP及Via光刻、刻蚀: (1)IMD淀积,CMP抛光:   (2)Via光刻、刻蚀,去胶:   13. Via-W plug淀积,CMP:基本与Conctact W-plug一样的做法;    14. Metal-2的淀积及Metal-2的光刻、刻蚀、去胶: (1)Metal-2淀积:  (2)Metal-2光刻刻蚀    15. 钝化层淀积及钝化层光刻、刻蚀、去胶:敦化刻蚀后一般要做一步alloy。    对于高级一点的工艺,可能会有更多层的metal,做法类似,继续Via和Metal的堆叠即可。 FinFET Process FlowThreshold System 有份公开资料介绍FinFET Process Flow,整理出来一起学习交流 1. Screen Oxide Growth 首先是P型衬底上面有一层外延生长的Si,厚度大概1um,然后再生长一层Screen Oxide(屏蔽氧化层。类似之前的pad oxide)。  2. N-Well and P-Well Definiton 定义N-Well和P-Well,左边区域进行硼离子注入,形成P-Well,右边区域进行磷离子注入,形成N-Well。  3. Photoresist Strip & Pad Oxide Growth 然后去除光刻胶和Screen Oxide,接着进行Rapid Thermal Anneal,修复晶格,活化P/N-Well,再生长一层Pad Oxide。  4. Silicon Nitride & Hard Mask Deposition 接下来的是Fin的形成,宽度大概10nm,普通的光刻工艺无法形成这么小的线框,这里用的是SADP工艺,通过sidewall space作为etch HM形成Fin,当然现在的EUV光刻机可以直接形成。 先是通过CVD工艺形成一层Silicon Ntride,上面再deposit一层Amorphous Carbon作为牺牲层,又称为Mandrel(保护层)。  5. Mandrel Patterning 接着coating BARC和PR进行曝光,形成Mandrel 的Pattern。  6. Mandrel Etch and PR Strip etch向下吃到Silicon Nitride层停止,然后去除PR,只留下Amorphous Carbon层。  7. Oxide Space Formation CVD工艺deposit一层Oxide Layer,然后etch向下吃Oxide到Silicon Nitride层停止,结果在Amorphous Carbon 侧边形成线宽很小的Oxide Spacer。  8. Mandrel Removal & Nitride Etch 然后通过etch 吃掉 Amorphous Carbon Mandrel层,只留下Oxide Spacer作为Hard Mask,然后再向下etch吃掉Silicon Nitride。  9. Fin Etch & Trench Liner Growth Oxide Spacer和Nitride作为Hard Mask继续向下etch,一直吃到P/N-Well层,然后通过热氧化在trench形成薄薄一层silicon dioxide,称为Trench Liner。  10. Trench Liner Removal & Fin Removal Photo 然后通过etch去除oxide trench liner,接着通过光刻胶,把P/N-Well中间的多余的Fin通过etch移除。  11. Fin Removal 多余的Fin移除前后对比图如下:  12. TEOS deposition 然后通过CVD填充一层厚厚的TEOS,接着通过CMP工艺研磨,直到接触silicon nitride停止。  13. Nitride Removal & TEOS Etch-Back 通过热磷酸溶液去除多余的silicon nitride,然后利用etch移除Fin周围的TEOS,剩下的Fin之间的TEOS作为STI(Shallow Trench Isolation)。  14. Alternate Well Implant Methodology 前面第2步已经通过离子注入定义了P/N-Well。如果没有定义,实际上到这一步也可以操作,工艺原理类似,通过光刻胶阻挡,分别进行离子注入。   15. ESL Growth & Amorphous Silicon Deposition 然后在Fin上通过热氧化生成一层oxide作为 etch stop layer(ESL),接着CVD deposit一层厚厚的Amorphous Silicon层。  16. Amorphous Silicon Depositon & Patterning 然后CMP磨平 Amorphous Silicon,接着CVD生长一层 Amorphous carbon做为Hard Mask,再deposit一层BARC做为抗反射层。  17. Hard Mask Patterning and Etch 曝光,Amorphous carbon 做为Hard Mask一直向下etch,P/N-Well 区域都留下Amorphous silicon的形状做为gate,实际上这是dummy gata,后面会remove,在填充high k介质和金属gate。  18. 2nd Gate Electrode Patterning 这一步主要是把右边多余的dummyGate去掉。   19. Offset Spacer Deposition 接下来先通过热氧化生成一层poly oxide,再通过CVD生成一层oxide,这两层就是所说的offset spacer。由于本文讨论的是replace gate制程,所以high-k电介质,metal gate,doped amorphous silicon gate electrode还没开始。  20. NMOS Extension Implant 铺上PR和BARC,然后进行litho和etch,使NMOS区域暴漏出来,再进行砷离子注入,使fin的表面形成一层Extension Implant区域。   21. PMOS Extension Implant 同理在PMOS区域进行硼离子注入。   22. Extension Anneal 由于离子注入后晶格有损失,接下来进行快速热退火工艺,活化PMOS/NMOS Extension。  23. Nitride Spacer Deposition Etch 接下来deposit一层silicon Nitride,然后进行etch,生成一层nitride spacers,Fin的两侧形成的spacer不是我们想要的,不过没关系,后面会移除。  24. Nitride Spacer Morphology Nitride Spacer形成后,我们可以看到dummy Gate Electrodes, Source, Drain区域的分布。  25. Hard Mask Deposition & Patterning 然后deposit一层SiCN做为Hard Mask,接着铺上BARC和PR进行曝光,目的是移除Fin。  26. Hard Mask Etch & PMOS Fin Removal SiCN作为Hard Mask,PMOS fin以及spacer全部被etch 完。  27. SiGe Deposition & Hard Mask Removal 接着进行SiGe外延生长,由于SiGe只会在Silicon表面生长,所以只在PMOS的Source/Drain Fin区域形成,然后etch剩下的SiCN hard mask。  28. Hard Mask Deposition & Patterning 同理,deposit一层SiCN Hard Mask,coating BARC和PR,接着在NMOS区域进行曝光形成图案。  NMOS区域有两种选择方案,一种是去除Fin上面的oxide后,外延生长Siliccon;另外一种是整体去除Fin,然后外延生长SiC,其目的都是增加载流子的迁移速率,下面分别介绍。 29. Hard Mask Etch & Oxide Strip NMOS 区域进行Hard Mask etch,然后用HF去除Fin上面的oxide。  30. #1 Epitaxial Si Growth Hard Mask Strip 然后在Fin上外延生长一层Si,也就是只会在NMOS的source/drain上形成,接着把多余的SiCN Hard Mask 移除。    31. #2 NMOS Fin Removal & SiC Epitaxial Deposition 将NMOS Fin全部移除,然后在Source/Drain区域外延生长SiC。  32. SiCN Hard Mask Strip & Silicon Implant 移除SiCN Hard Mask层,然后进行Silicon Pre-Amprphization Imlant(PAI),目的是形成一层均匀的,低电阻的silicide。  33. Oxide Strip & Al Salicide Implant 用HF移除Gate, Source, Drain上面的oxide,然后在PMOS区域进行离子注入Al,目的是降低SiGe表面的接触电阻。  34. Cold Titanium Deposition & Anneal 然后通过PVD的方式在表面形成一层Titanium,然后进行快速热退火,Titanium会在表面形成silicide。  35. Unreacted Titanium Strip 没有反应的Titanium位于spacer sidewall and STI上面,接着用湿法刻蚀的溶剂去除。  36. Oxide/Nitride Etch-Stop Laryer Deposition wafer用P/SC1溶剂清洗,然后在表面形成一层Silicon dioxide和nitride Silicon,将作为contact etch的stop layer。  37. PMD Deposition and Polish-Back 然后deposit一层厚厚的PSG(Phospho-Silicate Glass),这一层的作用是充当PMD(Pre-Metal-Dielectric),然后用CPM抛光,dummy gate上面的Nitride spacers将被磨掉,露出里面的amorphous silicon。  38. Polysiliocn Gate Removal 然后通过etch将dummy gate里的amorphous silicon移除,etch会停留在Fin上面的Oxide ESL。  39. Oxide ESL Removal 然后通过etch移除Fin上面的oxide layer。  40. Bottom Interface Oxide Layer Growth 然后通过低温氧化反应在Fin表面形成一层oxide,称为BIL(bottom interface layer),High-K电介质将会在上面生长。  41. High-k Dielectric Deposition 接下来ALD(Atomic Layer Deposition)工艺deposit一层High-k Hafnium oxide(氧化铪)做为电介质。   42. PMOS Metal(TiN) Deposition ALD工艺在PMOS区域deposit一层功函数金属gate TiN。   43. TaN Deposition 然后deposit一层TaN做为Etch Stop Layer。   44. PMOS Metal(TiN) Deposition 同理,再deposit一层TiN金属。   45. PMOS Metal Patterning 然后铺上一层PR,NMOS区域曝光露出来。   46. NMOS Metal Etch NMOS区域的TiN Layer被etch完,下面的TaN做为etch-stop layer。  47. Photoresist Strip 然后拔除PR,这里要注意,NMOS和PMOS区域的金属层是不同的。   48. NMOS Metal Deposition 然后通过SIPVD(Self Inoizing Phsical Vapor Deposition)工艺在NMOS/PMOS区域deposit一层TiAl金属。  49. NMOS Metal Anneal 在一定温度下,进行Anneal Metal,目的是使NMOS区域Al diffuse到High-k电介质的上方,形成TiAlN work function metal,而PMOS区域由于TiN做为阻挡层,Al不会diffuse进去。  50. Tungsten Deposition Back-Fill 然后deposit一层厚厚的金属钨,也是通过SIPVD工艺,金属钨会填充在Metal gate的空腔中。  51. Tungsten Metal Polish 然后CMP工艺磨平金属钨,可以看到gate空腔里面填充了金属钨,接下来就是contact连线工艺。  52. The FinFET Self Aligned Contacts 这里的contact用了SAC(Self-Aligned Contact)工艺,intel率先使用的,包括三步,etch--->deposition--->polish,下面会详细介绍。  53. Gate Metal Etch-Back 金属钨和Metal gate被etch back,露出空腔。  54. SiON Back-Fill 然后CVD deposit一层SiON,Gate空腔中也被填充。  55. SiON Polish-Back 下一步是通过CMP磨平,到PSG层停止,这样Gate空腔中填满了SiON。  56. PMD Completion 然后再deposit一层厚厚的PSG做为PMD(Pre-Metal Dielectri)  57. Tungsten Trench Contacts; Patterning 然后铺上PR,然后曝光定义连contact的区域,包括metal, source, drain区域,最后进行etch,打开金属层。  58.Ti/TiN Barrier Deposition 经过清洗干净后,然后通过IMP PVD工艺开始长Ti glue-layer,然后再长一层TiN,最后进行RTA,使Ti/TiN两层均匀的填充在contact区域。  59. Tungsten Deposition & Polish-Back 然后开始通过CVD deposit一层厚厚的金属钨,接着进行CMP磨平,这样gate, source, drain区域都通过金属钨contact连出来了。之前的工艺是用Cu做为contact连线,后面更先进工艺会用金属钴。  到此为止,FinFET工艺核心的前段,中段工艺介绍完毕,FinFET工艺较之前的平面MOS管工艺更复杂,每一步都有可能造成yield loss。

|

【本文地址】

今日新闻 |

推荐新闻 |